2026-03-03 03:13:37

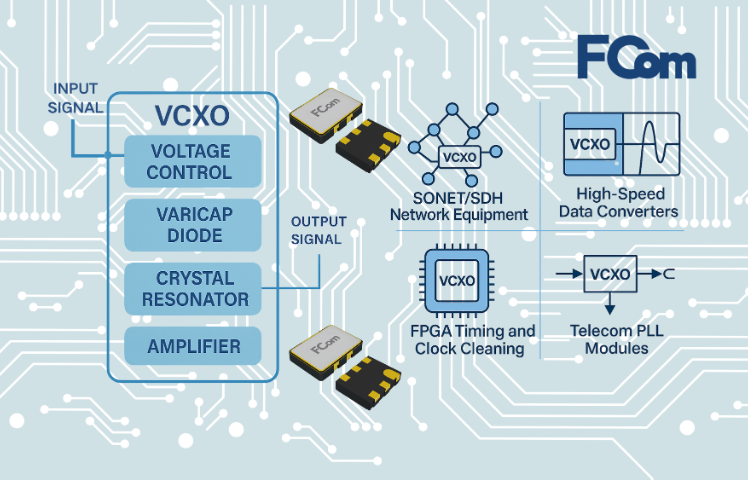

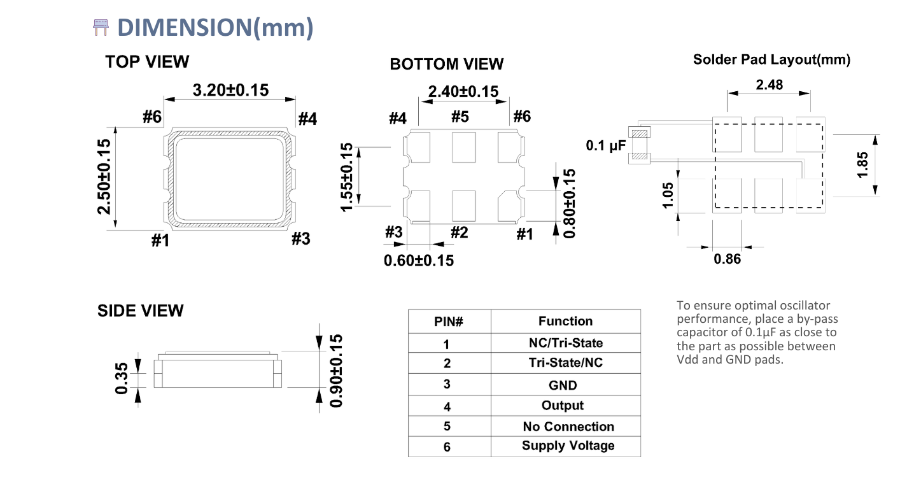

差分VCXO在數(shù)據(jù)存儲(chǔ)設(shè)備中的同步作用 在高性能數(shù)據(jù)存儲(chǔ)系統(tǒng)中,時(shí)鐘的穩(wěn)定性決定了數(shù)據(jù)傳輸?shù)臏?zhǔn)確性與一致性。尤其是在NAS、SAN、企業(yè)級(jí)RAID等系統(tǒng)中,多個(gè)硬盤或控制通道同時(shí)運(yùn)行,系統(tǒng)依賴差分VCXO提供精確的參考時(shí)鐘來(lái)避免數(shù)據(jù)錯(cuò)位與協(xié)議不匹配。 FCom富士晶振提供的差分輸出VCXO產(chǎn)品,支持LVDS和HCSL等主流差分接口,輸出頻率覆蓋25MHz、50MHz、100MHz、125MHz等多個(gè)檔位,適配Marvell、Broadcom等存儲(chǔ)控制芯片,保證主從控制之間的時(shí)鐘協(xié)同。 在數(shù)據(jù)寫入和讀取過(guò)程中,VCXO提供的可調(diào)頻特性(±50~100ppm)允許系統(tǒng)根據(jù)負(fù)載情況進(jìn)行頻率微調(diào),確保IO調(diào)度的效率和時(shí)序控制的精確性,尤其在多線程與緩存控制場(chǎng)景中發(fā)揮關(guān)鍵作用。 FCom產(chǎn)品封裝形式包括2520、3225等多種尺寸,具備抗振動(dòng)、耐高溫、低漏磁等特性,適用于高密度布線板卡和數(shù)據(jù)中心中低干擾要求的部署環(huán)境。 低至0.15ps的相位抖動(dòng)參數(shù)使FCom差分VCXO非常適合存儲(chǔ)設(shè)備中高速接口(如SATA/SAS/PCIe)中的時(shí)鐘系統(tǒng),確保整個(gè)存儲(chǔ)鏈路的誤碼率處于低水平。差分輸出VCXO在全光網(wǎng)絡(luò)與量子通信中亦有應(yīng)用前景。FVC5LPG差分輸出VCXO廠家電話

差分VCXO在SerDes高速鏈路中的同步作用 SerDes(串并轉(zhuǎn)換器)廣應(yīng)用于高速傳輸領(lǐng)域,如以太網(wǎng)、光纖通道、PCIe、USB等。FCom富士晶振差分輸出VCXO為其提供精確參考時(shí)鐘,確保鏈路建立與穩(wěn)定傳輸。 SerDes鏈路如Xilinx GTY、Intel Stratix、TI DS125BR系列通常采用100MHz或156.25MHz的差分時(shí)鐘源,F(xiàn)Com VCXO具備0.15ps以內(nèi)的RMS抖動(dòng),滿足眼圖和BER測(cè)試要求。 頻率拉動(dòng)能力支持±50~100ppm,便于進(jìn)行高速鏈路訓(xùn)練期間的動(dòng)態(tài)校準(zhǔn)與多通道偏移調(diào)整。 封裝尺寸覆蓋2520至7050,適配不同尺寸主板與高速背板設(shè)計(jì),且封裝抗串?dāng)_結(jié)構(gòu)有助于提升信號(hào)完整性。 差分輸出接口支持LVDS、LVPECL或HCSL,可靈活適配各種SerDes芯片標(biāo)準(zhǔn),為多通道同步提供標(biāo)準(zhǔn)時(shí)鐘接口。 FCom差分輸出VCXO在SerDes系統(tǒng)中是高速通信的基礎(chǔ)構(gòu)件,突出提升系統(tǒng)鏈路質(zhì)量和互聯(lián)性能。高穩(wěn)定差分輸出VCXO按需定制選擇差分輸出VCXO有助于降低系統(tǒng)抖動(dòng)。

差分VCXO為AI邊緣系統(tǒng)提供穩(wěn)定定時(shí)源 邊緣AI系統(tǒng)需要進(jìn)行本地?cái)?shù)據(jù)分析與模型推理,其內(nèi)部搭載的神經(jīng)網(wǎng)絡(luò)加速器、AI SoC及GPU協(xié)同模塊依賴統(tǒng)一時(shí)鐘源進(jìn)行高速協(xié)作。差分VCXO正是這些多模塊平臺(tái)理想的同步方案。 FCom富士晶振支持100MHz、125MHz、156.25MHz頻率,適配如NVIDIA Jetson Orin、Hailo-8、Kneron KL730等邊緣推理芯片的時(shí)鐘輸入接口。 低抖動(dòng)(